# Performance Analysis of Power Factor Correction for PWM Control based Bridgeless Cuk Rectifier with Positive Output Voltage

M.Valan Rajkumar, J.Chandramohan, D.Aravind, M.Basker

Department of Electrical and Electronics Engineering, Gnanamani College of Technology, Namakkal-637018, India.

Abstract – This paper presents a single-phase, bridgeless Cuk AC/DC power factor correction (PFC) rectifier with positive output voltage. The rectifier is designed to convert high input voltage to low output voltage which is used for low output voltage product applications. There is the input conduction losses are decreased due to no bridge-diodes required, so the proposed rectifier efficiency can be improved. The proposed rectifier does not need the current loop circuit it needs discontinuous conduction mode (DCM) only. Also, only a single switch is used in the rectifier to simplify the control circuit design. A simple translation method to have the positive output voltage in the Cuk converter is presented in the rectifier to reduce the component counts and the cost as well. The operational principles, steady-state analysis, and design procedure of the proposed rectifier are addressed in detail in this paper. Simulation and experimental results are obtained which verified the validity of the proposed rectifier.

Index Terms – Power factor correction (PFC), Discontinuous conduction mode (DCM), bridgeless, Cuk, positive output voltage.

#### 1. INTRODUCTION

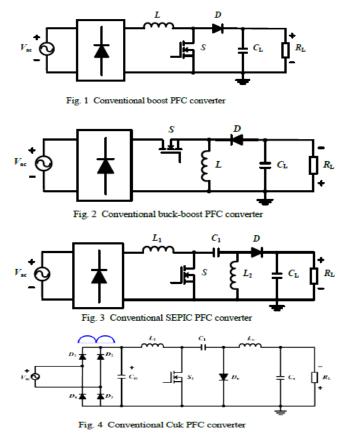

In recent years, switched-mode power supply technologies have developed rapidly. Most switched mode power supplies for electronic products are used to convert AC to DC sources in different applications. The use of a transformer, a bridge rectifier, and capacitors can achieve a DC-output voltage easily, but the input current may be seriously distorted. Therefore, the PFC converters are critically required for AC-DC conversion [1-2]. A variety of circuit topologies have been developed for the PFC applications. The conventional PFC converter is a full bridge rectifier followed by a boost converter, as shown in Fig. 1. The converter is widely used, because of its simplicity. However, due to boosting behavior of the converter, the output voltage is always greater than the input voltage. In many applications, such as low voltage and low-power supplies, it is desired to have the output voltage lower than the peak of input voltage. A buck-type converter is thus required. The buck converter is seldom used in the PFC application, since as the input current of the buck converter is discontinuous, it would lose control when the input line-voltage is lower than the output voltage. The renewable energy is used to track maximum power point and multilevel inverters are used to convert DC-AC for various applications [3-9]. Also, to filter the input current, additional passive filter must be used at the buck converter input. Many algorithms are used to give gate generations [10-13].

Besides, the buck PFC converter may lead to increased total harmonic distortion (THD) and reduced power factor (PF) [14]. Therefore, in such applications, converters like buck-boost, single ended primary inductor converter (SEPIC) or Cuk converter are often used next to a full-bridge rectifier, as shown in Fig. 2 to Fig. 4 [15-23], to have a PFC converter with low output voltage.

All the converters mentioned above can be used in DCM or continuous conduction mode (CCM). While operating in DCM to shape the input current sinusoidally, these converters have intrinsic PFC characteristics at fixed duty ratio [14], there is no need of any control circuit. However, the drawbacks of buckboost converter operating in DCM are high-current stress on semiconductor devices and discontinuous input current, which increases the THD.

On the other side, SEPIC and Cuk converters are the ones whose input currents are continuous, while operating in DCM with the output voltage lower than the input voltage. Similar to the boost converter, SEPIC converter has the disadvantage of discontinuous output current, resulting in relatively high output ripple.

The Cuk converter offers several advantages in PFC applications, such as easy implementation of transformer isolation, natural protection against inrush current occurring at start-up or overload current, lower input current ripple, and less electromagnetic interference (EMI) associated with the DCM topologies.

Unlike the SEPIC converter, the Cuk converter has both continuous input and output currents with a low current ripple. Thus, for applications requiring low-current ripples at the both input and output ports of the converter, the Cuk converter seems to be a better candidate in the basic converter topologies.

In practical applications the DCM operation of the Cuk converter significantly increases the conduction losses, due to the increased current stress on the circuit components. However, using CCM for low-power applications, it requires extra components to achieve PFC performance. As a result, additional circuit cost is increased. This limits the DCM operation of the Cuk converter only in low-power applications (< 300 W).

In a conventional PFC Cuk rectifier as shown in Fig. 4, the current flows through bridge diodes and the power switch (*S*1) during the switch ON-time, and through bridge diodes and the output diode (*D*0) during the switch OFF-time. Thus, during each switching cycle, the current flows through three power semiconductor devices. As a result, the significant conduction loss caused by the forward voltage drop across the bridge diodes degrades the converter's efficiency, especially at low line-input voltage. To reduce the conduction losses, the number of semiconductor devices should be reduced in the current path. Some methods to reduce conduction losses in Cuk and SEPIC converters are proposed.

The control circuits are complex using two main switches in the Cuk PFC topology. The bridgeless SEPIC converter introduced in [18] consists of two SEPIC converters, each of which is used for a half-line cycle. Thus, the number of devices and the cost are increased. As mentioned above, the SEPIC converter has the disadvantage of discontinuous output current, resulting in a relatively high output ripple.

The Cuk and SEPIC converters have negative output voltages. Therefore, the extra requirement is an inverse amplifier circuit to translate the negative into the positive voltage. The additional inverse amplifier circuit thus increases the cost.

# 2. PROPOSED BRIDGELESS CUK PFC RECTIFIER WITH POSITIVE OUTPUT VOLTAGE

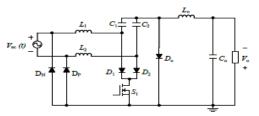

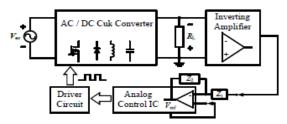

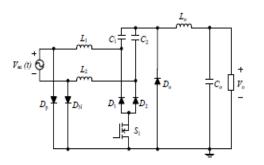

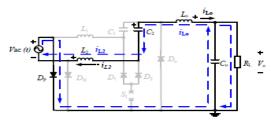

Fig. 5 shows the proposed initial bridgeless Cuk PFC rectifier, which has a negative output voltage, like the existing Cuk PFC rectifier. As noted, for this circuit an inverting circuit to transfer the negative to the positive output voltage is still required for analog feedback control, as shown in Fig. 6.

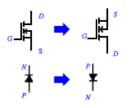

To obtain the positive output voltage without the inverting amplifier circuit, we transfer the polarity of all the components in Fig. 5 into those as shown in Fig. 7, and obtain the proposed bridgeless Cuk PFC rectifier in Fig. 8. Thus, the feedback control circuit is simpler and the cost can also be reduced, as compared with the conventional feedback control circuit as shown in Fig. 6, though the power switch employed in the proposed circuit is floated with a high-side gate driver needed.

Fig. 5 Proposed Bridgeless Cuk power factor correction rectifier with negative output voltage

Fig. 6 Blocking Diagram of the conventional Cuk PFC circuit (with negative output voltage)

Fig. 7 Transferring the polarity of all components in the proposed initial topology in Fig. 5

Fig. 8 Proposed Bridgeless Cuk PFC rectifier with positive output voltage

Before analyzing the proposed rectifier, the analysis of the circuit supposes that the converter is operating at steady state with the following assumptions:

1. The ON-state resistance RDS\_ON and parasitic capacitances of the main switch S1 and the forward voltage drops (Vd) of the diodes are neglected.

2. The input capacitances are large enough such that during a switching period (Ts) their voltages are considered to be constant.

3. The output capacitor Co is sufficiently large that the output voltage is considered to be constant.

4. The proposed converter is operated in the DCM.

5.Due to symmetry of the circuit, it is sufficient to analyze the circuit during the positive half-cycle of the input voltage.

#### A. Principles of Operation

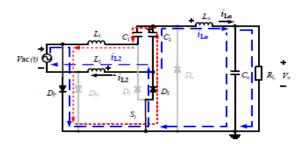

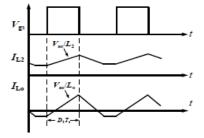

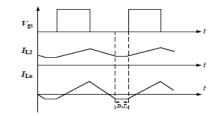

Mode I [t0 - t1]: This mode starts when switch S1 is turned ON, as shown in Fig. 9 and Fig. 10. Input inductors L2 starts to charge linearly in slope of Vac(t)/L2, and diode Dp is forward biased by the indictor current iL2. The voltage across Lo is equal to Vac(t), thus iLo increases linearly in slope of Vac(t)/L0. The inductor currents of L2 and L0 during this mode are given by

$$Di_{Ln}/dt = v_{ac}(t)/L_{n}, n = 2,0$$

(1)

Accordingly, the peak current through the active switch S1 is given by

$$Is1_{,pk=(Vm/Lo)}D_1T_s$$

<sup>(2)</sup>

whereVm is the amplitude of the input voltage Vac(t), D1 is the switch duty cycle, and Le is the parallel combination of inductors of L1, L2, and Lo.

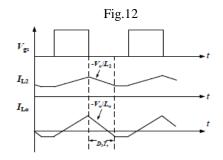

Mode II [t1 - t2]: This mode starts when switch S1 is turned OFF and diode Do is turned ON, simultaneously, as shown in Fig. 11 and Fig. 12. Input inductor L2 starts to discharge linearly in slope of Vac(t)/L2, and diode Dp is forward biased by the indictor current iL2. The voltage across Lo is equal to

Vo, thus iLo decreases linearly in slope of Vo/Lo. Note that diode Do is turned OFF at zero current. The inductor currents of L2 and Lo during this mode are given by

$$Di_{L2}/dt = (-V_{ac}(t)/L2)$$

(3)

Fig. 9 The equivalent circuit in mode I (Switch S1 is turned ON)

Fig. 10 Theoretical DCM waveforms during one switching period  $T_i$  in mode I (Switch  $S_1$  is turned ON)

Fig. 11 The equivalent circuit in mode II (Switch S<sub>1</sub> is turned OFF)

Fig. 12 Theoretical DCM waveforms during one switching period T<sub>s</sub> in mode II (Switch S<sub>1</sub> is turned OFF)

$$Di_{Lo}/dt = (-Vo/L0)$$

(4)

# International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 5, Issue 4, April (2017) www.ijeter.everscience.org

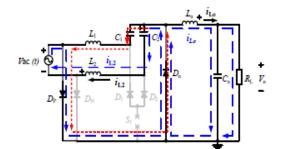

Mode III [t2 - t3]: During this interval, only diode Dp conducts to provide a path for *i*L2, as shown in Fig. 13. Accordingly, the inductors L2 and Lo in this interval behave as constant current source. Thus, the voltage of inductors (L2 and Lo) is zero. Capacitor C2 is being charged by the inductor current *i*L2 and the energy of capacitor C is released to load.

This is a freewheeling mode. The theoretical waveforms in this mode are shown in Fig. 14. This mode lasts until the start of a new switching period. The turn-OFF time of the switch and the output diode is given by

$$t_{\rm off} = T_{\rm s} - t_{\rm don} \tag{5}$$

whereton is the conducting interval of switch S1 and tdon is that of the output diode Do.

According to Equations (2) and (4), the normalized length of Mode II period can be obtained as follows:

$$D_2 = D1/m \sin \omega t$$

(6)

where  $\omega$  is the line angular frequency, and *M* is the voltage conversion ratio (M = Vo/Vm).

# B. Analysis and Design of the Proposed Cuk PFC Rectifier

### (1) Design of Input Inductors

According to the relationship of input current ripple ( $\Delta IL2$ ), as shown in Fig. 10, and input voltage (Vac) in positive-half cycle, the values of input indictor (L1 and L2) can be obtained below:

$$L2=Vac(t)D1/\Delta I_{L2}f_s$$

(7)

#### (2) Voltage Conversion Ratio M

The voltage conversion ratio M in terms of the rectifier parameters can be obtained by applying the power-balance principle below,

Fig. 13 The equivalent circuit in mode III (Switch S1 is turned OFF)

Fig. 14 Theoretical DCM waveforms during one switching period  $T_s$  in mode III (Switch  $S_1$  is turned OFF)

$$P_{in}(t) = 2/T \int V_{in}(t) I_{in}(t) dt$$

(8)

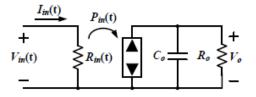

According to the large-signal model of the DCM switch network, as shown in Fig. 15, it is noted that the average input current can be given as follows:

$$I_{in}(t) = V_{in}(t)/R_{in}$$

<sup>(9)</sup>

Where *Rin* is defined as the input resistance and given by

$$R_{in} = 2L_{e}/D_{1}^{2} T_{5}$$

(10)

Evaluating (8) by using (9) and applying the power balance between the input and output ports, the voltage conversion ratio can be given by

$$M = V_o / V_m \tag{11}$$

(3) Boundaries between CCM and DCM

To operate in DCM, the following inequality must be satisfied:

$$D_2 = <1 - D1$$

(12)

Substituting Equation (6) into (12) and applying (10) and (11), the following condition for DCM is obtained:

$$K_{e} \leq K_{e \operatorname{cri}} = 1/2(M + \sin(\omega t))^{2}$$

(13)

where the parameter Ke is expressed as follows:

$$K_e = 2L_e/R_lT_s \tag{14}$$

It is obvious that from Equation (13) the value of  $Ke_{crit}$  depends on the line angle  $\omega t$ . Thus, the minimum and maximum parameters of  $Ke_{crit}$  can be obtained, respectively:

$$K_{e-cri(min)} = 1/2(M+1)^2$$

(15)

$$K_{e-cri(min)} = 1/2M^2$$

(16)

Therefore, for *K*e<*K*e\_crit(min), the proposed bridgeless Cuk PFC rectifier with positive output voltage always operates in DCM.

#### (4) Selection of Input Capacitors

In the Cuk converter as PFC, voltages of the input capacitors C1 and C2 should be nearly constant value within the switching period Ts and follow the input voltage profile within a line period TL. Also, the input capacitors C1 and C2 should not cause low-frequency oscillations with the converter inductors. Thus, the energy transfer capacitors C1 and C2 are determined based on inductor L1, L2 and Lo values such that the line frequency (fL) should be well below the switching frequency (fs). And a better initial approximation for choosing the resonant frequency (fr) is given by (17) and (18).

$$f_l < f_r < f_s \tag{17}$$

$$f_r = 1/2\pi (c_1(L_1 + L_0))$$

(18)

Fig. 15 Large signal model [18] of the proposed Cuk PFC rectifier

#### (5) Design of Output Capacitor Co

Output ripple frequency of the converter is two times of the input frequency. In the worst case, the output current during the half period of ripple frequency is provided by the output capacitor. Therefore, *Co* can be obtained as follows:

$$C_0 = P_0 / 4 f_1 V_0 \Delta V_0 \tag{19}$$

#### (6) Stresses on Semiconductor Devices

According to Fig. 11, we may derive the following expressions about the stresses on semiconductor devices as functions of input/output voltages and currents on inductors.

$$V_{D,max} = V_{sw,max} = V_{ac,max} + V_0$$

(20)

where VD,max and ID,max are the maximum voltage and current stresses on diodes Dp, Ds, D1, D2 and Do; Vsw,max and Isw,max are the maximum voltage and current stresses on switches S1, respectively; Vac,max and Iac,max are the maximum input voltage and current;  $\Delta IL$  is the current ripple of L1 or L2, and IL2,min is the minimum current of L2.

#### 3. EXPERIMENTAL RESULTS

By following the specification given in Table I and the design procedure described above, components and parameters used in the proposed power-stage circuit are listed in Table II for verification of the proposed rectifier.

The experimental results show that *S*1 turns on under ZCS condition and *D*0 turns off under ZCS condition, as shown in Fig. 14 to Fig. 16, respectively. Therefore, reverse recovery problem of the main diode is resolved by employing the proposed Cuk rectifier in DCM.

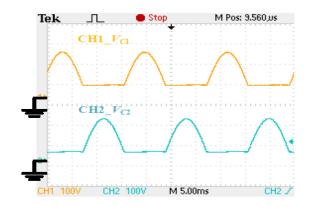

The experimental results of the input voltage and current waveforms are shown in Fig. 11 to Fig. 15 for 20%, 50%, 80% and full (150W) loads, respectively. Fig. 18 shows the experimental waveforms of capacitors C1 and C2 at full load.

As shown in Fig. 10 for the measured current harmonics, it can be observed that the IEC 61000-3-2 Class D limits of the current harmonics are well met by the proposed Cuk rectifier. The experimental results of the PF and the THD values of the input current for different loads of 20% to full loads (*V*in=110Vrms). The PF is about 0.9961 and the THD in percentage of the input line current is 2.66% for the full power output of 150 W. Since the proposed rectifier has the functions of ZCS turn On and ZCS turn-off (for the output diode), the switch and output diode losses can be significantly decreased at full load. The measured efficiency from 20% to full loads of the prototype rectifier at line voltages of 90 Vrms, 110 Vrms, and 130 Vrms are shown. It reveals that all the efficiencies of different loads for the line voltage of 110 Vrms are above 91%. The best efficiency 96.2% is obtained at high line-voltage of 130 Vrms at full load, and the worst efficiency 89.7% is observed at low line-voltage (90 Vrms) for 20% load.

| TABLE I                                 |                         |  |

|-----------------------------------------|-------------------------|--|

| SPECIFICATION OF THE PROPOSED RECTIFIER |                         |  |

| Specifications                          |                         |  |

| Input Voltage V <sub>in</sub>           | 90-130 V <sub>rms</sub> |  |

| Output Voltage Vout                     | 48 V <sub>dc</sub>      |  |

| Rated Power Pout                        | 150 W                   |  |

| Switching Frequency <i>f</i> ₅          | 100 kHz                 |  |

|              | TABLE II                                               |                  |

|--------------|--------------------------------------------------------|------------------|

| COMPONENT PA | ARAMETERS USED IN THE                                  | PROPOSED CIRCUIT |

| Device       | Component                                              | Part/Value       |

| Power Switch | Main Switches S <sub>1</sub>                           | IXFH3650P        |

|              | Input Diodes $D_p$ and $D_n$                           | MBR20200CT       |

| Diodes       | Series Diodes $D_1$ and<br>$D_2$<br>Output Diode $D_0$ | STTH6003CW       |

| Inductors    | Input Inductors $L_1$ and $L_2$                        | 1 mH             |

|              | Output Inductor $L_{o}$                                | 22 uH            |

| Capacitors   | Input Capacitors<br>C1 and C2                          | 1 uF/400V        |

| •            | Output Capacitor Co                                    | 2 mF/100V        |

| Control IC   | UC 3525 (Voltage mode)                                 |                  |

The comparisons of test conditions and power components are used between the proposed circuit and the one. As shown in the table, the inductor used in the proposed circuit is smaller than the one in under same rated power output.

Fig. 16 Experimental waveforms of VC1 and VC2 at full loadS1 at full load (150 W)

In addition, for the same output voltage of 48 Vdc the efficiency 96.2% of the proposed circuit at full load of 150W

www.ijeter.everscience.org

with input voltage of 130 Vrms is compared to 93.2% at full load of 150W with input voltage of 100 Vrms [18] and 93.0% at full load of 100W with input voltage of 220 Vrms. Since the efficiencies available from the experimental results in the literature are for different power output ratings and input voltages of the circuits compared, only the efficiencies at their full loads are compared as above. However, it should be noted that the comparisons are only for references, due to different test conditions and components employed in the circuits.

# 4. CONCLUSIONS

In this paper, the Cuk PFC rectifier with positive output voltage has been proposed and experimentally verified. The experimental results have shown good agreements with the predicted waveforms analyzed in the paper. The power factor of the circuit has 0.99 above at all the specified input and output conditions. Satisfaction of the IEC 61000-3-2 requirements can be easily achieved by the proposed circuit. Moreover, with higher efficiency and high power factor the proposed topology is able to be applied to most of the consumer electronic products of 150W rating in the market. Also, with only a single switch employed, the implemented system control circuit is simple to achieve high power factor by applying any PWM control IC. Moreover, as required in the traditional Cuk circuit, transferring the original negative output voltage to the positive one is not needed in the proposed Cuk topology. Convenience of using the Cuk rectifier can thus be obtained.

#### REFERENCES

- M. Mahdavi and H. Farzanehfard, "Bridgeless SEPIC PFC Rectifier with Reduced Components and Conduction Losses," IEEE Transactions Industrial Electronics, vol. 58, No. 9, pp. 4153-4160, Sep. 2011.

- [2] Y. Jang and M. M. Jovanovic, "Bridgeless High-Power-Factor Buck Converter," IEEE Transactions Power Electron, vol. 26, No. 2, Feb. 2011.

- [3] M.ValanRajkumar, P.S.Manoharan, Modeling and Simulation of Threephase DCMLI using SVPWM for Photovoltaic System, Springer Lecture Notes in Electrical Engineering, under the volume titled "Power Electronics & Renewable Energy Systems", Volume 326, Chapter No 5, January 2015, Pages 39-45.

- [4] M.ValanRajkumar, P.S.Manoharan, Harmonic Reduction of Fuzzy PI Controller based Three-Phase Seven-level DCMLI with SVPWM for Grid Connected Photovoltaic System, Journal International Review on Modeling and Simulations, Volume 6, No 3, June 2013, Pages 684-692.

- [5] A.Ravi, P.S.Manoharan, M.ValanRajkumar, "Harmonic Reduction of Three-Phase Multilevel Inverter for Grid connected Photovoltaic System using Closed Loop Switching Control", Journal-IREMOS, Volume 5, No 5, October 2012, Pages 1934-1942. ISSN: 1974-9821 (Print), 1974-982X (Online)

- [6] P.Thirumurugan, P.S.Manoharan, M.ValanRajkumar, "VLSI Based Inverter Switching Control" in the proceedings of International Conference on Mathematical Modeling and Applied Soft Computing MMASC'12 – Coimbatore Institute of Technology on July 2012, Vol-2 (Page):965-973.

- [7] C.Hemalatha, M.Valan Rajkumar, G.Vidhya Krishnan, "Simulation and Analysis for MPPT Control with Modified firefly algorithm for photovoltaic system", International Journal of Innovative Studies in Sciences and Engineering Technology, Volume 2, No 11, Nov.2016, Pages 48-52.

- [8] G.Vidhya Krishnan, M.Valan Rajkumar, C.Hemalatha, "Modeling and Simulation of 13-level Cascaded Hybrid Multilevel Inverter with less

number of Switches", International Journal of Innovative Studies in Sciences and Engineering Technology, Volume 2, No 11, Nov.2016, Pages 43-47.

- [9] M.ValanRajkumar, P.S.Manoharan, FPGA Based Multilevel Cascaded Inverters with SVPWM Algorithm for Photovoltaic system, Elsevier Journal Solar Energy, Volume 87, Issue 1, January 2013, Pages 229-245.

- [10] B. Sanjay Gandhi, S. Sam Chelladurai, and Dr. D. Senthil Kumaran, "Process Optimization for Biodiesel Synthesis from Jatropha Curcas Oil", Taylor & Francis-Distributed Generation and Alternative Energy Journal, Vol.23, No.4, Page 6- 16, 2011.

- [11] B. Sanjay Gandhi and D. Senthil Kumaran, "The Production and Optimization of Biodiesel from Crude Jatropha Curcas Oil by a Two Step Process— An Indian Case Study Using Response Surface Methodology", Taylor & Francis-International Journal of Green Energy, Vol.113, No.10, Page 1084-1096, 2014.

- [12] M.ValanRajkumar, P.S.Manoharan, Space Vector Pulse Width Modulation of Three-Phase DCMLI with Neuro-Fuzzy MPPT for Photovoltaic System, World Journal of Modelling and Simulation, Volume 10, No 3, August 2014, Pages 193-205.

- [13] M.Valan Rajkumar, Prakasam, P. and Manoharan, P.S. (2016) Investigational Validation of PV Based DCDMLI Using Simplified SVM Algorithm Utilizing FPGA Tied with Independent Sources. Circuits and Systems, Volume 7, No 11, 3831-3848. http://dx.doi.org/10.4236/cs.2016.711320

- [14] R. Oruganti and M. Palaniapan, "Inductor Voltage Control of Buck Type Single-Phase AC-DC Converter," IEEE Transactions Power Electronics, vol. 15, No. 2, pp. 411-416, Mar. 2010.

- [15] M. A. Al-Saffar, E. H. Ismail, and A. J. Sabzali, "Integrated Buck Boost– Quadratic Buck PFC Rectifier for Universal Input Applications," IEEE Transactions Power Electronics, vol. 24, No. 12, pp. 2886-2896, Dec. 2009.

- [16] P.Thirumurugan, P.S.Manoharan, M.ValanRajkumar, VLSI Based Space Vector Pulse Width Modulation Switching Control in the proceedings of IEEE International Conference on Advanced Communication Control and Computing Technologies ICACCCT 2012 on August 2012, ISBN No. 978-1-4673-2045-0 (Print) (Page):366-370.

- [17] M.ValanRajkumar, P.S.Manoharan, "Modeling, Simulation and Harmonic Reduction of Three-Phase Multilevel Cascaded Inverters with SVPWM for Photovoltaic System", Journal International Review on Modeling and Simulations, Volume 6, No. 2, April 2013, Pages 342-350. ISSN: 1974-9821 (Print), 1974-982X (Online)

- [18] M.ValanRajkumar, P.S.Manoharan, "Modeling and Simulation of Fivelevel Five-phase Voltage Source Inverter for Photovoltaic Systems", Journal PrzegladElektrotechniczny, Volume 10, No. 10, October 2013, Pages 237-241. ISSN: 0033-2097 (Print)

- [19] T. Ching-Jung and C. Chern-Lin, "A Novel ZVT PWM Cuk Power Factor Corrector," IEEE Transactions Industrial Electronics, vol. 46, No. 4, pp. 780-787, Aug. 1999.

- [20] D. S. L. Simonetti, J. Sebastian, and J. Uceda, "The Discontinuous Conduction Mode Sepic and Cuk Power Factor Preregulators: Analysis and Design," IEEE Transactions Industrial Electronics, vol. 44, No. 5, pp. 630-637, Oct. 1997.

- [21] S. Chandrasekar and Gian Carlo Montanari, "Analysis of Partial Discharge Characteristics of Natural Esters as Dielectric Fluid for Electric Power Apparatus Applications," IEEE Transactions on Dielectrics and Electrical Insulation, Vol. 21, No. 3, pp.1251-1259, June 2014.

- [22] V.Jayaprakash Narayanan, B.Karthik and S.Chandrasekar," Flashover Prediction of Polymeric Insulators Using PD Signal Time-Frequency Analysis and BPA Neural Network Technique," Journal of Electrical Engineering and Technology. Vol. 9, Issue 4, pp. 1375-1384, 2014

- [23] P. F. de Melo, R. Gules, E. F. R. Romaneli, and R. C. Annunziato, "A Modified SEPIC Converter for High-Power-Factor Rectifier and Universal Input Voltage Applications," IEEE Transaction Power Electronics, vol. 25, No. 2, pp. 310-321, Feb. 2010.